Difference between revisions of "Digital Sidecar"

| Line 25: | Line 25: | ||

*The 14 general purpose digital input/output (GPIO) channels connect directly to the NI9403 module. There is a 10K pullup resistor on each line, so an unconnected pin will read as a "1" level. For the same reason, a limit switch that uses one of these inputs should be connected between the signal pin and GND, so that when the switch is open, it reads a "1". | *The 14 general purpose digital input/output (GPIO) channels connect directly to the NI9403 module. There is a 10K pullup resistor on each line, so an unconnected pin will read as a "1" level. For the same reason, a limit switch that uses one of these inputs should be connected between the signal pin and GND, so that when the switch is open, it reads a "1". | ||

*The Output_enable signal is "active low," meaning that outputs are enabled when it drives a "0". When this signal is a "1", the PWM (Victor, Jaguar, servo) and relay (spike) controls turn these devices off. | *The Output_enable signal is "active low," meaning that outputs are enabled when it drives a "0". When this signal is a "1", the PWM (Victor, Jaguar, servo) and relay (spike) controls turn these devices off. | ||

| − | *There are 14 PWM signals, each driven through a buffer than can be disabled. There is a 330 ohm resistor in series with each line, effectively providing isolation from short circuits and other bad connections on the electrical board. The pulse width modulated waveform is generated by the cRIO FPGA controlled by the PWM class in the software. [PWM_Details] | + | *There are 14 PWM signals, each driven through a buffer than can be disabled. There is a 330 ohm resistor in series with each line, effectively providing isolation from short circuits and other bad connections on the electrical board. The pulse width modulated waveform is generated by the cRIO FPGA controlled by the PWM class in the software. [[PWM_Details]] |

Revision as of 18:37, 8 November 2011

The Digital Sidecar is the most complex FIRST-supplied breakout in the control system, providing the following functions:

- power input reverse voltage protection with circuit breaker

- power input indicator light

- 5 and 6 volt power supplies

- FRC friendly physical connections

- NXT port to enable use of Mindstorms components

- serial to parallel conversion for driving relays (spike)

- general purpose digital IO with pullups for digital inputs.

- buffered PWM outputs for motor controllers (victor and jaguar) and servos

- optional 6v power for servos

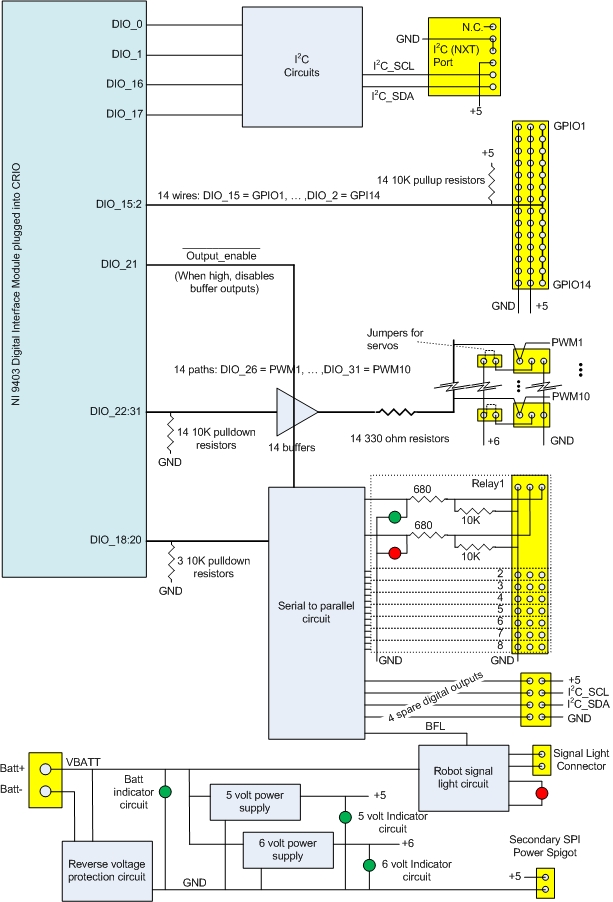

The block diagram below shows all of the circuits and their connections to the battery and the cRIO NI9403 32 channel digital interface module. The software components for motor controls, etc, interface with most digital components, relays and motor controllers utilize this module. The detailed schematic of the digital sidecar from Worcester Tech is available here.

This block diagram is a simplified version of the detailed schematics, including only enough detail to show the key circuit blocks, but also with details like pullup and limiting resistors to guide design of robot components that utilize the digital sidecar.

Starting at the top of the block diagram:

- The I2C circuits provide an interface for NXT (Lego Mindstorms) components. This enables using FTC and FLL sensors.

- The 14 general purpose digital input/output (GPIO) channels connect directly to the NI9403 module. There is a 10K pullup resistor on each line, so an unconnected pin will read as a "1" level. For the same reason, a limit switch that uses one of these inputs should be connected between the signal pin and GND, so that when the switch is open, it reads a "1".

- The Output_enable signal is "active low," meaning that outputs are enabled when it drives a "0". When this signal is a "1", the PWM (Victor, Jaguar, servo) and relay (spike) controls turn these devices off.

- There are 14 PWM signals, each driven through a buffer than can be disabled. There is a 330 ohm resistor in series with each line, effectively providing isolation from short circuits and other bad connections on the electrical board. The pulse width modulated waveform is generated by the cRIO FPGA controlled by the PWM class in the software. PWM_Details